Selected by Alpha Metallurgical Resources to design a wireless sensor network for real-time data transmission in underground coal mining environments as part of the University of Alabama Senior Capstone Program.

- Designed and implemented a low-latency (<5 ms), high-throughput (~100 Mbps) dual-band (2.4 GHz / 5 GHz) network under harsh underground conditions

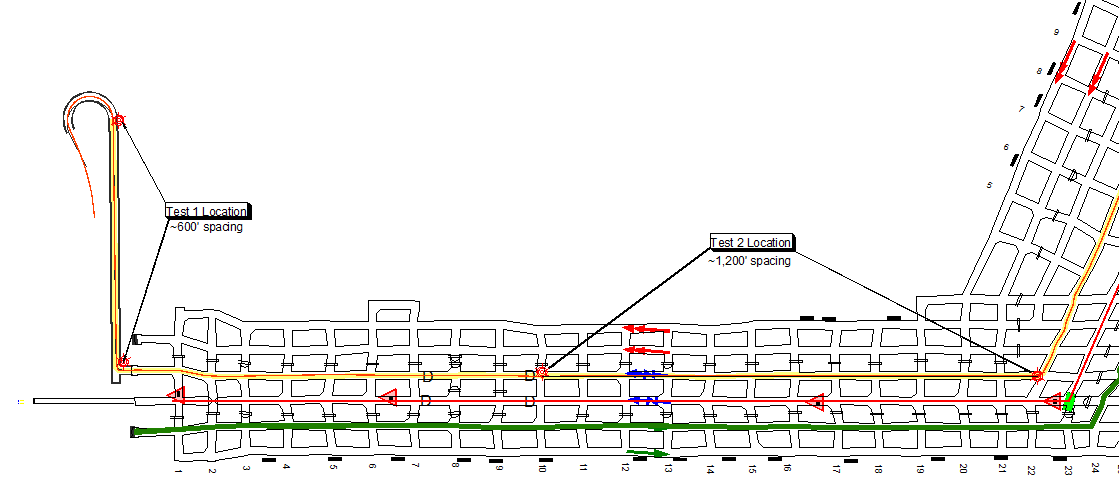

- Ensured reliable communication in non-line-of-sight tunnel environments

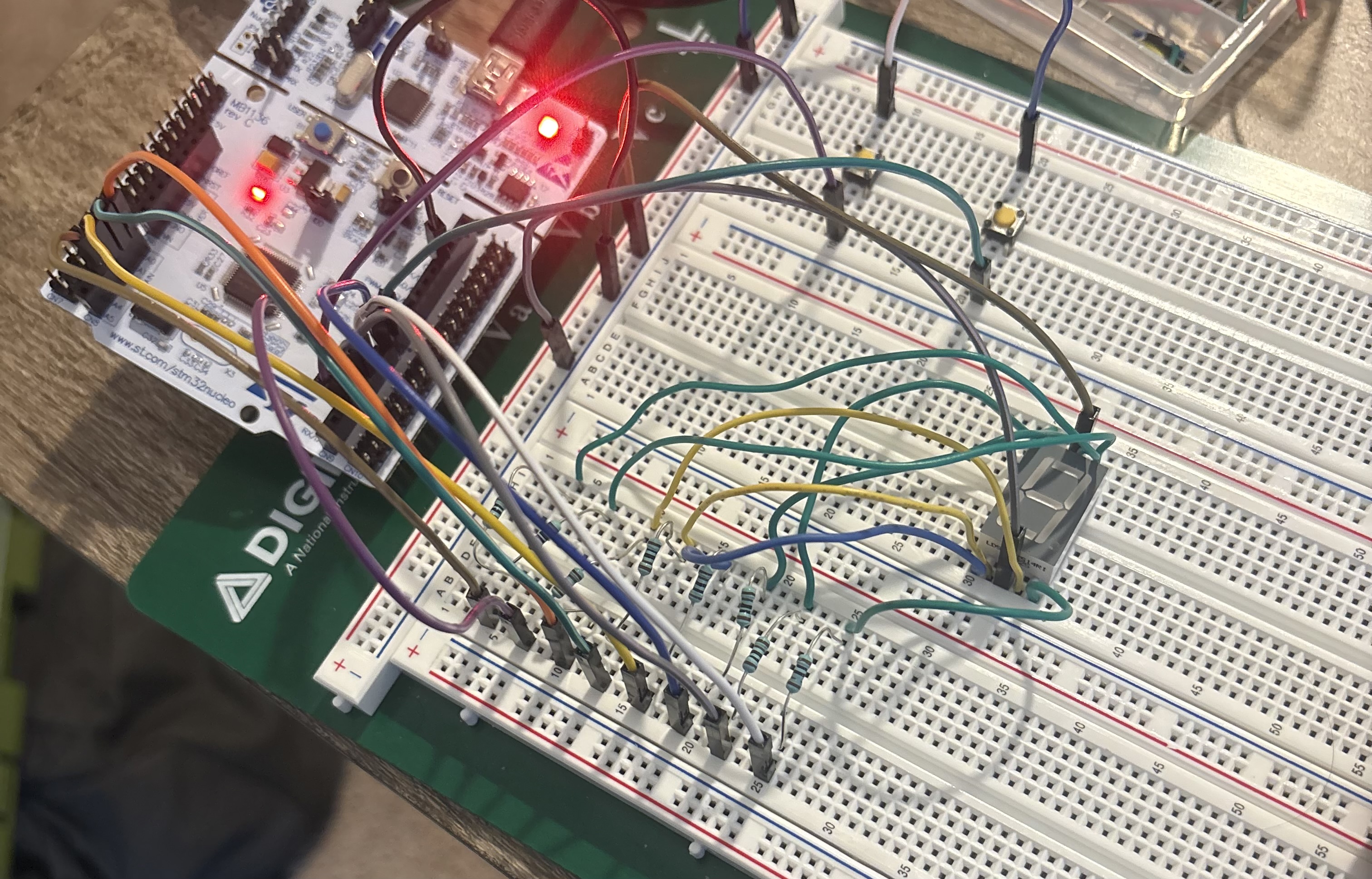

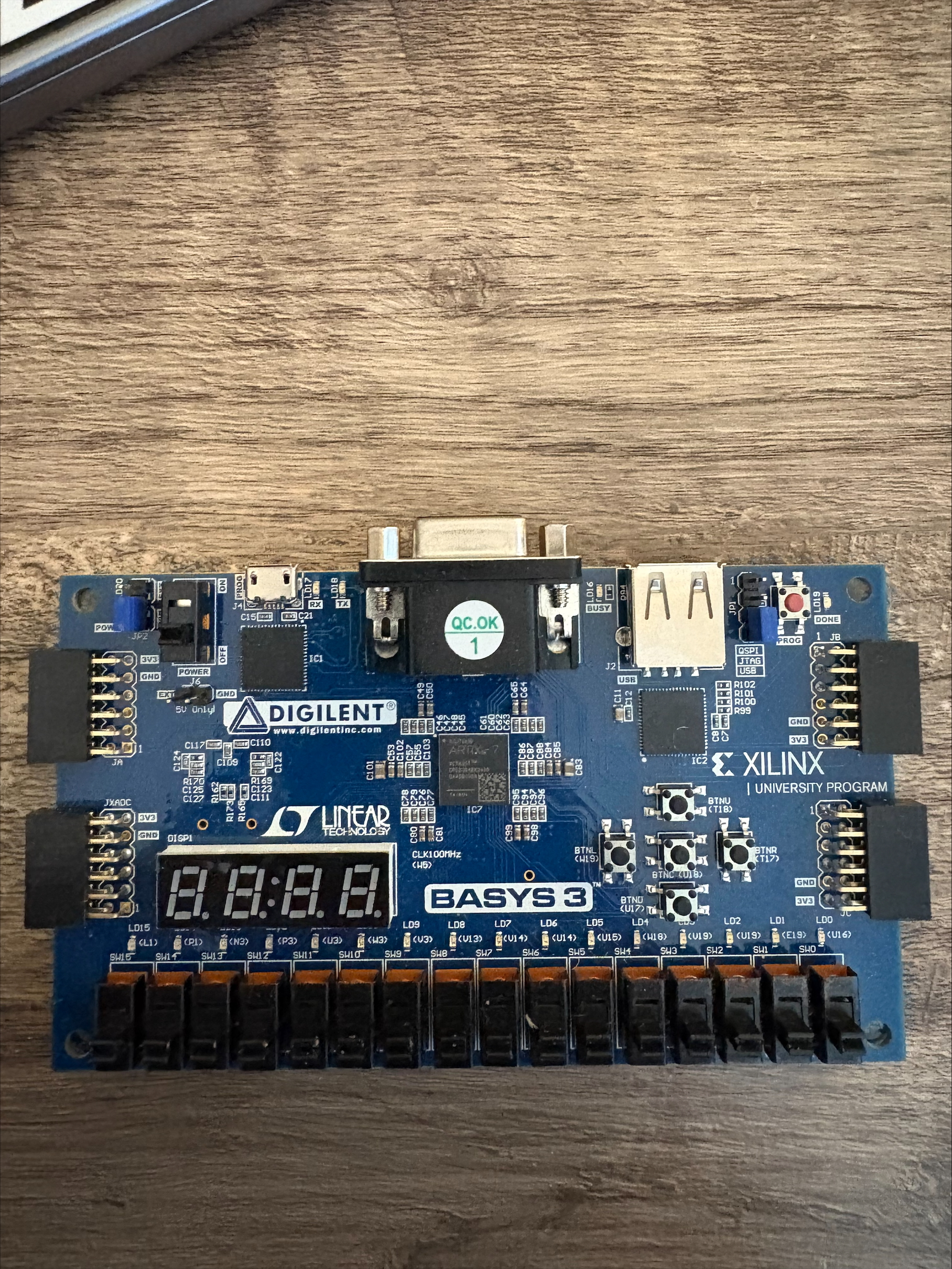

- Collaborated with industry engineers, faculty advisors, and a multidisciplinary team of four on system architecture, component selection, and deployment strategy

- Conducted on-site testing in an active underground mine, identifying and mitigating challenges including RF interference, airlocks, and competing mesh networks

- Validated system performance with zero packet loss in constrained underground environments

/Screenshot%202026-04-10%20112712.png)

/Screenshot%202026-04-10%20113003.png)

/Screenshot%202026-04-10%20113035.png)

/Screenshot%202026-04-10%20112902.png)

/Screenshot%202026-04-10%20112618.png)